现货库存:1000

FPGA作为有史以来最具创新性的半导体器件,一直都走在架构和工艺的最前沿。也正是因其较高的技术门槛和IP要求,这一领域的玩家几乎屈指可数。两家主流的FPGA厂商在架构创新和工艺制程的提升方面你追我赶,竞争甚是激烈。不过,这一局面开始呈现出一些新的发展态势,几年的攻城掠地后,他们都在自己所专注且擅长的领域赢得了一席之地,差异化特征越来越明显。

赛灵思在忙什么?

这是我非常关注的一个问题。

赛灵思的创新,让赛灵思从传统可编程逻辑公司转型为“All Programmable”公司,创建各种形式的软/硬件、数字和模拟可编程技术并将其并整合到All Programmable FPGA、SoC和3D IC中。这些器件集可编程系统的高集成度以及嵌入式智能和灵活性于一身,支持快速开发高度可编程的智能系统。

有两个动向需特别关注:赛灵思推出“软”定义网络(“Softly” Defined Networks)解决方案,将可编程能力和智能化功能从控制层扩展至数据层。全新SDNet软件定义规范环境可实现可编程数据层功能设计,而且功能规范可自动编译到赛灵思的All Programmable FPGA和SoC中。

赛灵思又宣布推出针对OpenC++L、C和C++的SDAccel开发环境,将单位功耗性能提高达25倍,相对其它FPGA解决方案,性能和资源效率可提高3倍。目前,赛灵思已经通过这一开发环境实现了FPGA向数据中心应用加速。

赛灵思究竟在做什么?它的发展路线始终围绕FPGA,但似乎已经超越了传统FPGA厂商的范畴。以下节选自美国Eletronic Engineering Journal的一段内容或许对我们有所启发。

If FPGAs are to become the compute engines of the future, the flow of FPGA design must make a tectonic shift toward the software engineer. The devices must seem like processors, and the implementation must feel like programming. Synthesis, simulation, and layout must be replaced by compilation and debug. Detailed control of optimization options must be replaced by rapid iteration and productive workflow. In short, the whole hardware-engineer-centric FPGA process must be turned on its side.(from Kevin Morris at EE Journal)

这就是赛灵思正在做的事情。

单纯地依靠FPGA芯片架构、工艺制程或是增强型工具套件进行性能提升已成为过去式。如果FPGA希望进入一个更广阔的新世界去开疆拓土,软件开发环境是一个不得不逾越的鸿沟,而这需要根本上的改变。赛灵思必须能够在硬件工程师与软件开发人员之间搭建起一座沟通的桥梁,让他们即使使用各自的语言也能自由沟通。

SDNet是Xilinx的第一步尝试,SDAccel则紧随其后。这就是赛灵思努力实现的SDx系列,它已不仅仅是某一项市场策略,而是该公司以软件为中心的SDx生态系统,正在帮助赛灵思将FPGA的发展推进一个新境界。当然,背后起关键支撑作用的仍然是赛灵思多年来大量的工具和IP积累。

赛灵思如何搭建软硬件人员的沟通桥梁?

建立起硬件工程师与软件开发人员的沟通并非易事。硬件工程师追求的是系统的优化——如何在最小的硅片面积,以最低的功耗,实现最佳的性能。而软件开发人员则注重如何有效管理复杂代码,他们通常需要面对成千上万行代码,必须快速地进行迭代、分析,并以最少的bug、最易理解的方式来组织他们的编程语言。二者的工作似乎永远不会有交集。赛灵思是如何实现的?

SDAccel技术是建立在赛灵思于2011年年初收购AutoESL时获得的高层次综合(HLS)技术的基础上实现的。赛灵思在过去三年多时间里进一步开发该技术,并将其作为产品供货给1000多名FPGA客户。与此同时,赛灵思还将该技术从针对C和C++扩展到了现在能够优化本地OpenCL代码的编译工作。

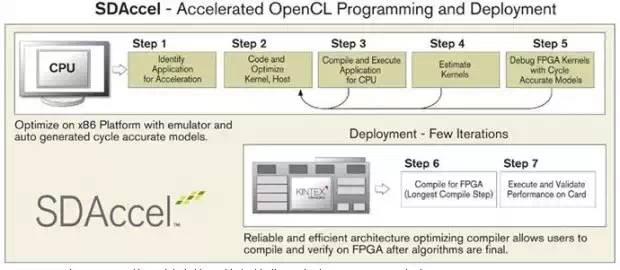

SDAccel使软件开发人员能够利用新的或现有的OpenCL、C和C++ 代码创建高性能加速器,并针对计算搜索、图像识别、机器学习、编码转换、存储压缩和加密等各种数据中心应用中的存储器、数据流和流水线技术进行了精心优化。图1给出了SDAccel环境中的典型设计流程。

图1:通过SDAccel编译创建的可执行镜像可在赛灵思FPGA中实现。

有FPGA实例化经验的软件开发老手会发现SDAccel中有很多熟悉的内容。允许C、C++和OpenCL输入是为了让来自独立CPU领域的开发人员尽快熟悉编程环境,同时能获得FPGA的所有独特功能集。SDAccel支持在CPU上的完整仿真,程序员可对并行和流水线化元素进行比较,并在对特定FPGA架构进行初始编译之前执行循环、片上存储器、和数据流等优化操作。

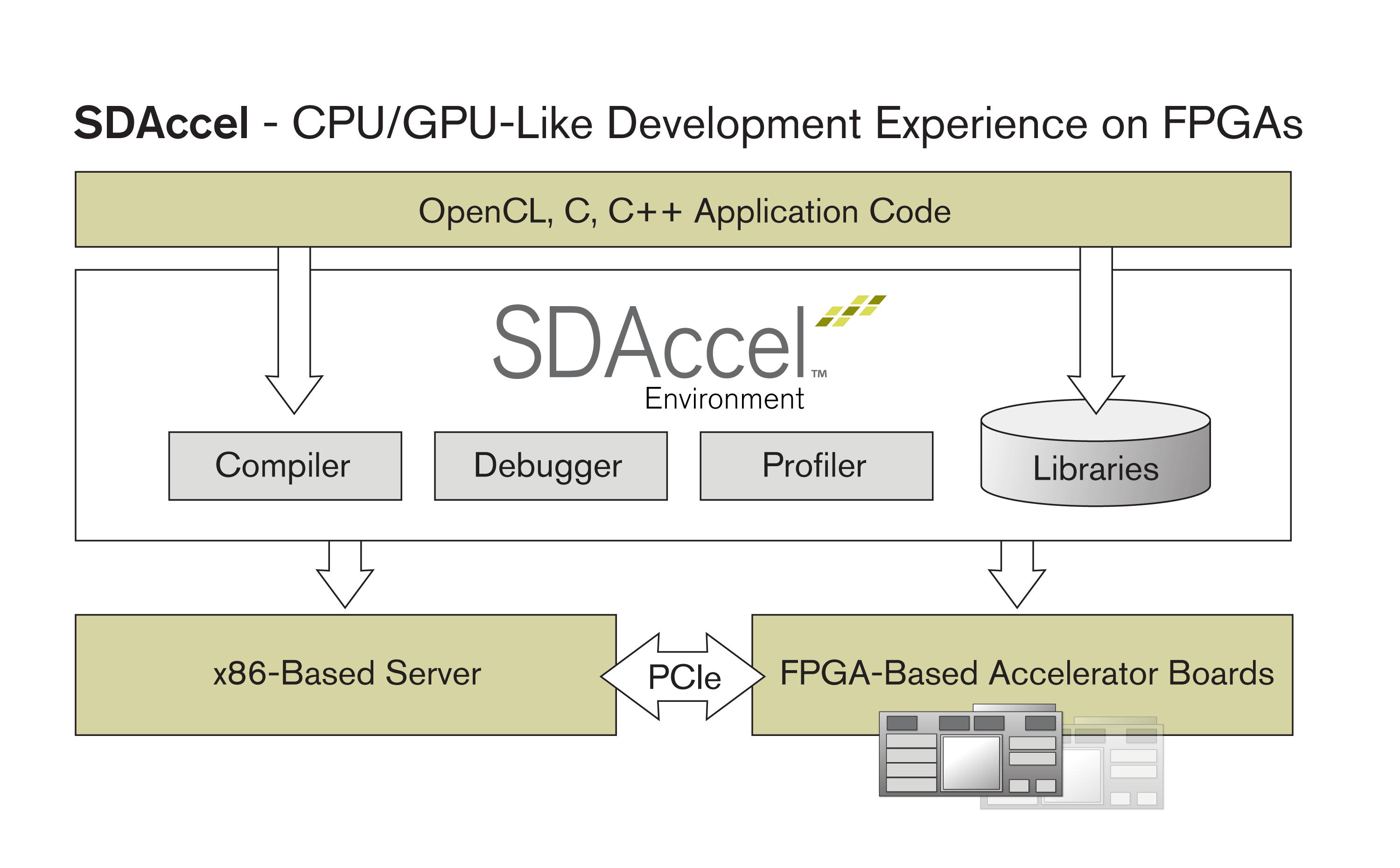

在FPGA上首次实现完全类似CPU/GPU的开发体验

借助SDAccel,开发人员能够使用其熟悉的工作流程优化应用,而且即便之前没有FPGA使用经验,也能受益于FPGA平台的优势。集成设计环境(IDE)不仅可提供编码模板和软件库,而且还能对各种开发目标进行编译、调试和特性分析,如在X86平台上仿真、使用快速仿真进行性能验证以及在FPGA处理器上进行本地执行等。IDE可在数据中心用FPGA平台上执行应用。该平台配套提供面向所有支持开发目标的自动仪器插入功能。此外,SDAccel还经过精心设计,使CPU/GPU开发人员能够轻松将其应用迁移到FPGA上,同时还可在他们熟悉的工作流程中维护和复用OpenCL、C和C++代码。

综合全面的SDAccel环境包括编程器用IDE、基于C语言的FPGA优化库,以及数据中心用现成商用(COTS)平台。

SDAccel库包括用于高性能低功耗实现方案的内置OpenCL函数、DSP、视频以及线性代数库。针对特定领域加速,赛灵思联盟合作成员Auviz Systems提供了精心优化的OpenCV和BLAS OpenCL兼容型软件库。原有的COTS成员包括Alpha Data、Convey、Pico Computing,预计2015年年初还将增加更多成员。

图2:SDAccel开发环境包括架构优化编译器、库、调试器以及特性分析器,可提供类似CPU或GPU的编程体验

在FPGA上首次实现完全与CPU/GPU的运行时间体验

SDAccel能够支持带有多个程序和类似CPU / GPU按需可加载计算单元的应用。与CPU/GPU类似,SDAccel对于FPGA解决方案的独特之处,在于能够保持程序转换过程中的系统正常工作。SDAccel目前是业界唯一能够创建可在应用运行过程中加载新加速器内核的FPGA计算单元的环境。在整个应用执行过程中,存储器、以太网、PCIe和性能监控器等关键系统接口和功能均保持工作状态。即时可重配置的计算单元可让多个应用共享FPGA加速器。例如通过对运行系统编程,可支持图像搜索、视频转码和图像处理之间的切换。

能够支持C、C++和OpenCL对开发人员来说是一个独特优势,因为无论是使用现有代码库还是利用全新的OpenCL环境都可达到“两全其美”境地。尽管OpenCL提供一些明显优势,例如可移植性,以及在主机与运行内核的计算单元之间实现代码分段,但是大部分函数库和现有代码库均采用C或C++编写。SDAccel使客户能够在合适的时候继续用C和C++进行开发,同时利用OpenCL的可移植性进行移植。

SDAccel库包含OpenCL内置函数、DSP、视频和线性代数库。SDAccel还将诸如OpenCV和BLAS等第三方的库集成到其软件环境中。当设计方案使用压缩或加密等复杂协处理模块时,利用SDAccel开发环境得到的设计在性能和大小方面可与手动编码效果旗鼓相当,甚至更胜一筹。

面向未来数据中心的开发环境

一直阻碍FPGA在数据中心应用中更广泛使用的主要原因就是缺乏一款高效优化的编译器和相关开发环境,以满足数十年在面向通用CPU和GPU架构的编译器上工作的需求。SDAccel的出现终于打破了这一局面,有助于在数据中心应用中实现设计优化。

SDAccel不仅可完成用户在任何本地OpenCL编译器上所能实现的基本功能,如循环合并、扁平化以及展开等,而且还能执行一些更高级的优化工作,如内存使用、数据流、循环流水线等选项。这些优化让客户通过编译器将C、C++或OpenCL直接高效导入到FPGA硬件中。赛灵思基准测试显示,编译器相对优化的RTL大小可减少5%,而且在一些情况下其结果质量(QoR)相比RTL能提升20%以上。这让客户能够在具有嵌入式调试功能的本地FPGA硬件上进行综合和调试前,即可在架构层的x86处理器上设计和优化他们的应用。

SDAccel不仅使加速内核接近传统CPU和GPU,甚至超越它们以往的性能,而且还能简化面向未来低功耗异构数据中心的FPGA产品的开发工作。SDAccel在为数据中心创建功耗更优化型计算环境,以及在通用开发环境中整合 CPU/GPU优化型编译和动态可重配置加速器方面所起的重要作用。

SDx系列仍在持续创新

赛灵思公司亚太区销售与市场副总裁杨飞表示,赛灵思的SDx系列仍会持续发展。毫无疑问,这会帮助赛灵思面向更为广泛的用户群。事实上,不仅是数据中心,未来,有线通信、无线通信等领域都有广阔的应用前景。

赛灵思SDx系列已经收获了一系列不错的反响。关于它的未来,关于FPGA的未来,会是很有趣的猜想。

应用案例:

百度现已转用深度神经网络(DNN)处理技术来解决语音识别、图像搜索以及自然语言处理中存在的各种问题,这是因为他们已经认识到,当在线预测使用神经反向传播算法时,FPGA解决方案远比CPU和GPU更容易进行扩展。

板级超级计算机专家Convey Computer将x86 CPU与赛灵思FPGA结合,设计了一款可帮助数据中心服务器进行内容高速缓存的Wolverine加速卡。Convey与戴尔的数据中心解决方案(DCS)业务部通力合作推出了一款图像缩放解决方案(在社交媒体和图片存储网络中非常需要)。该解决方案采用两个Virtex7开发板,相对仅采用CPU的同等系统而言,缩放速度可提高35到40倍。此外,Convey-Dell解决方案之所以得到广泛使用,关键还是能够利用更高级的语言定制FPGA加速器。

微软于今年年初启动了一项计划——使用FPGA加速Bing搜索排名。微软公司服务器工程副总裁Kushadra Vaid最近在Linley处理器大会上的一次主题演讲中展示了使用1632台带PCIe FPGA加速卡的服务器试生产结果。相对于未加速的服务器,微软实现方案的吞吐量提高了2倍,而时延和成本分别降低了29%和30%。

戴尔公司平台架构与技术及CTO 办公室执行总监Robert Hormuth指出:“基于FPGA的技术有了新的突破,能支持优化的计算应用。在戴尔服务器部署的过程中,简化编程是决定采用FPGA加速器的关键障碍。。毫无疑问,赛灵思开辟了一条正确的道路,让开发人员能够借助一个软件环境,提高FPGA平台用户的生产力。”

IBM电源开发副总裁兼OpenPOWER基金会总裁(IBM vice president of Power Development and OpenPOWER president)Brad McCredie表示:“IBM坚信OpenCL对提高生产力大有裨益,正在与赛灵思展开紧密合作,将该技术应用到我们的OpenPOWER产品设计中。”

---> END <---